Very Large Scale Integration Lab

The prime objective of this laboratory to give a compact idea about recent trends in digital system design, ASIC design and FPGA based hardware design and implementations. Now a day, the high-speed communication channels requires peripheral devices with higher data processing capability with minimum latency. FPGA based system is an attractive choice for this purpose. Again, semi-custom/programmable design style in FPGA based design reduces the design time, complexity and cost. The hardware description language (HDL) such as Verilog is widely used for FPGA development due to its simplicity and design portability and cross-platform in nature. Apart from that, this lab gives a fair idea about CAD tool used for analog design which basically starts from transistors

Faculty In-charge:

Prof S .Padhy

Technical Asst. In-charge:

Mrs. Asmita Pattnaik

| SL.NO. | Name of the Equipments | Model/Type | Make | Quantity | Location |

| 1 | Cadence | VERSION-2016 | 30 | VLSI LAB | |

| 2 | Mentorgraphics | VERSION-2017 | 50 | VLSI LAB | |

| 3 | SYNOPSIS SENTARUS TCAD software | VERSION-2018 | 7 | VLSI LAB | |

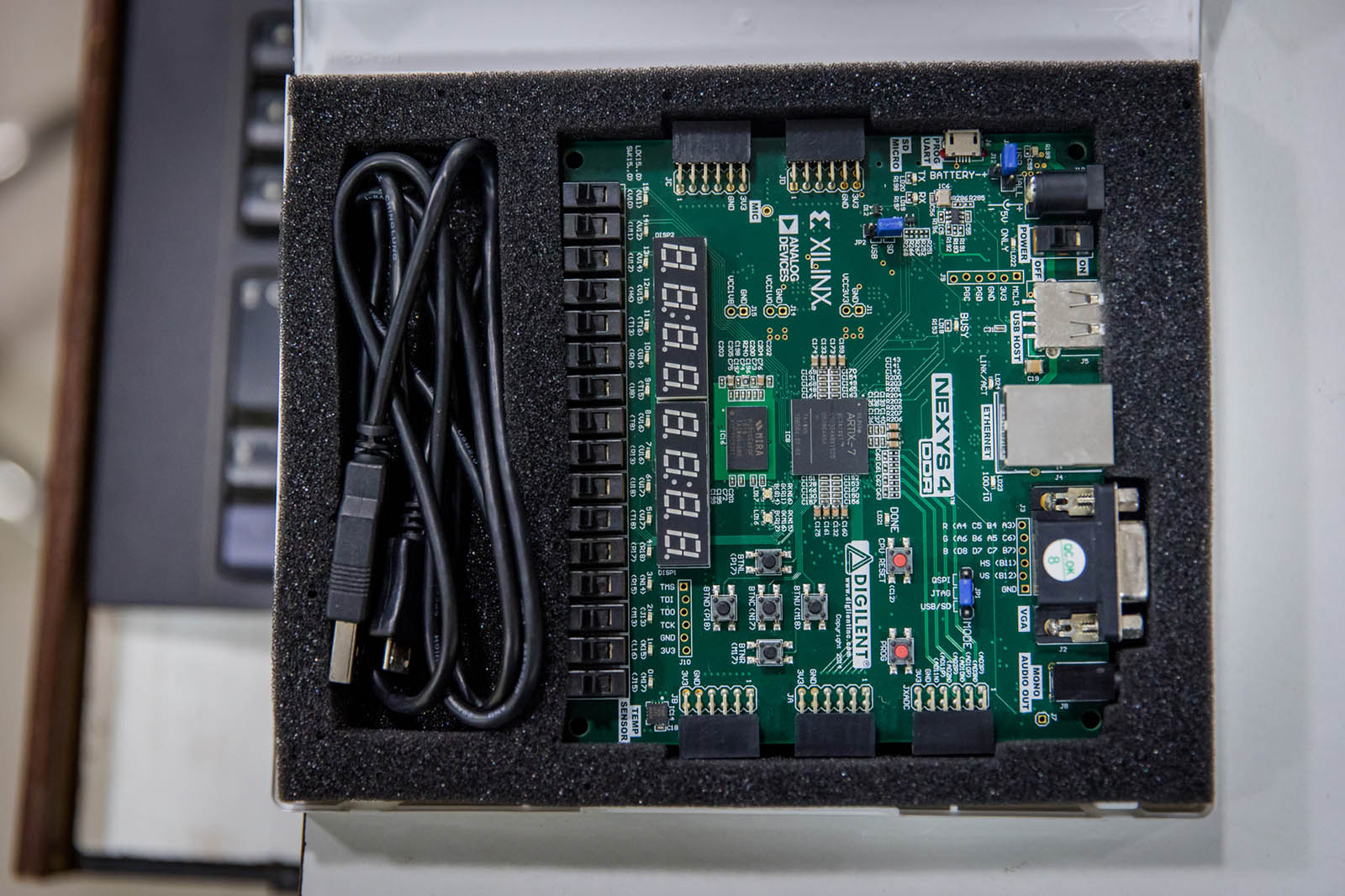

| 4 | Spartan 6 board | XC6STX-25T | 40 | VLSI LAB | |

| 5 | Artix 7 Nexys 4 DDR board | ARTIX | COREAL TECHNOLOGIES | 30 | VLSI LAB |

| 6 | Zynq 7000 board | ZYNQ | KINTEX | 15 | VLSI LAB |

| 7 | Xilinx Vivardo Software | VERSION 2017 | COREAL TECHNOLOGIES | 50 | VLSI LAB |