## SUMMER TRAINING 2025

## Program Details

Design and Implementation of a RISC-V Core on an FPGA

## **Course Objective**

No Lodging

KIIT Affiliation

Continuous Evaluation

Hybrid Mode

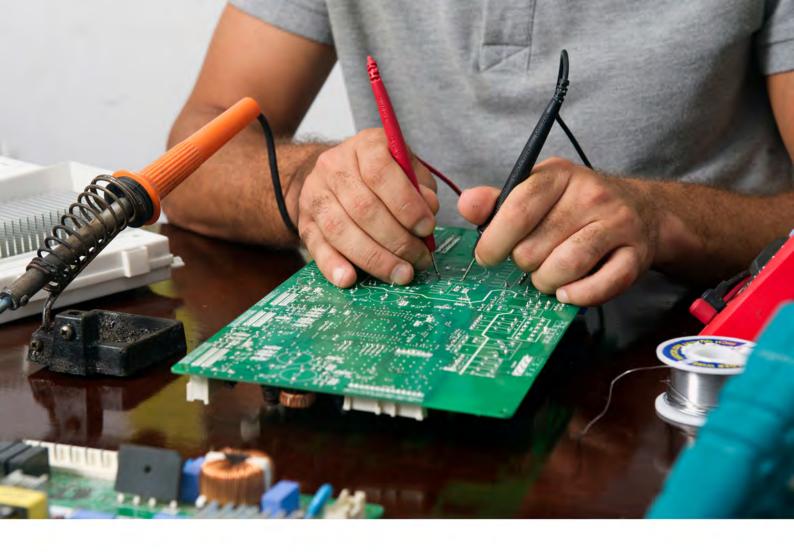

This course provides a comprehensive exploration of RISC-V core design and FPGA implementation. Students will learn to translate architectural specifications into synthesizable hardware using HDLs like Verilog. Practical exercises will cover memory interfacing and peripheral integration. By the end, students will be able to design, simulate, and deploy a functional RISC-V core on an FPGA platform, gaining valuable skills in embedded system development and hardware acceleration. The course emphasizes hands-on experience and real-world application of RISC-V principles.

### **Course Outcome**

01

Students will successfully develop and demonstrate a working RISC-V processor core on an FPGA, capable of executing basic programs and interacting with peripherals

02

Students will demonstrate proficiency in using hardware description languages (Verilog) and FPGA synthesis tools to translate architectural designs into implementable hardware.

03

Students will be able to integrate a RISC-V core with memory and peripherals, debug hardware and software interactions, and analyze system performance on an FPGA platform.

| Section                | Details                                    |

|------------------------|--------------------------------------------|

| Course Duration (Hrs)  | 40 + Project (20)                          |

|                        | KIIT Affiliation: Rs. 4000/-               |

| Course Fee             | Other Affiliation: Rs. 5000/-              |

|                        | (No Fooding & Lodging)                     |

| Teaching Learning Mode | Hybrid Mode                                |

|                        | Dr. Jitendra Kr. Das                       |

| Course Instructors     | Dr. Sarita Nanda                           |

|                        | Dr. Subir Kr. Maity                        |

| Course Evaluation      | Continuous Evaluation                      |

| Course Certificate     | After successful completion of the course. |

## Module Descriptor for the Course

#### Module - I

Fundamentals of Computer Architecture and RISC-V.

Von Neumann Architecture, CPU, Memory, I/O, Instruction Set Architecture (ISA), Register, Memory Addressing. History and Philosophy of RISC-V, Advantages of RISC-V, RISC-V Specifications (Base ISA, Extensions), RV321, RV641, and other common extensions.

#### Module - II

RISC-V Base Integer Instruction Set (RV32I): Register Conventions, Arithmetic Instructions (ADD, SUB, MUL, DIV), Logical Instructions (AND, OR, XOR), Shift Instructions (SLL, SRL, SRA), Immediate Instructions.

Memory access instructions: Load (LB, LH, LW), store (SB, SH, SW), addressing modes.

Control flow instructions: branch instructions (BEQ, BNE, BLT, BGE), jump instructions (JAL, JALR), basic assembly programs (e.g., Sum of Numbers, Factorial), intro to assembly language calling conventions.

#### Module - III

Verilog HDL fundamentals: Introduction to Verilog HDL, gate level, data flow and behavioral modeling style, and arithmetic and logical operators in Verilog.

Concatenation operator and ternary operator. Procedural block, ifelse, and case statement in Verilog. Memory design (RAM) in Verilog. Design of finite state machines (FSM) (Mealy type) with an example (3-bit sequence detector). Implementation of a simple 8-bit ALU using dataflow and behavioral modeling style and its testing using a testbench.

# Module Descriptor for the Course

Implementing a Basic RISC-V Core in Verilog and testing Basic Core Architecture (Fetch → Decode → Execute → Writeback), Designing the Instruction Memory. Implementing a Basic ALU for Addition & logical operations, Implementing a simple RISC-V core in Verilog, and testing it with a basic addition/subtraction instruction. and modify the core to support logical operations. Connecting Instruction Memory to the Core. Simulating the core with a test bench. Load the hex file into the Verilog Core and verify the execution of an assembly program in Verilog. Modify the RISC-V Verilog core and testbench to store the output in memory and verify correctness.

Introduction to RISC-V GCC toolchain: Toolchain setup, writing a C code, and generating a HEX file. Loading the HEX file into the generated RISC-V Verilog core and testing it with a testbench. Sample program: addition of a series of numbers, factorial, multiplication using functions.

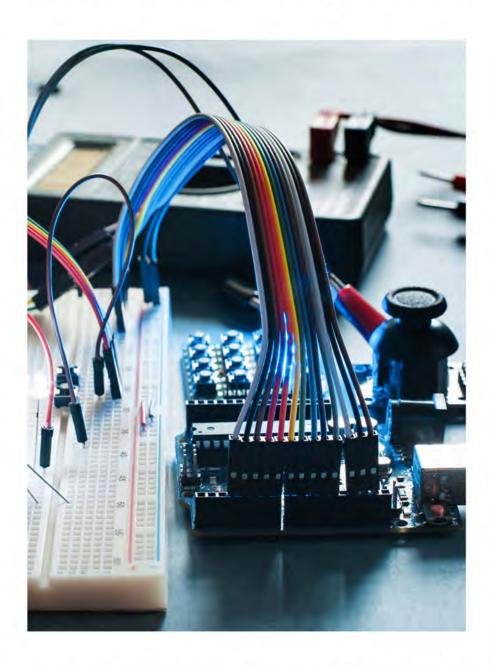

Adding GPIO peripheral to RISC-V core: Adding LEDs and switches to the RISC-V core. Test the core for GPIO operation. FPGA implementation of the core with GPIO support.

### Contact Us

School of Electronics Engineering, Campus-12, KIIT

Dr. J. K. Das, (+91 79 78 253 530) Dr. S. Nanda (+91 63 70 085 277) Dr. S. K. Maity (+91 89 84 266 431)

compliance.electronics@kiit.ac.in dean\_electronics@kiit.ac.in electronics.helpdesk@kiit.ac.in